nor flash调试与使用总结

最近项目中使用到norflash,总结一下学习与使用经验

文章目录

- 一、Flash基本概念

- 存储器介绍与Flash在其中定位---非易失存储器类别中嵌入式领域常见设备

- Flash的典型分类---NorFlash(贵/容量小/读快写慢)与NandFlash(便宜/容量大/读慢写快)

- Flash的基本 存储和 读 写 擦原理---电荷是否超过特定阈值来表示0(低表示1)

- 二、nor flash关键特性理解(以 GD25Q128介绍)

- 基本特性介绍---容量、访问接口、读写速度、擦除性能、写保护

- 【关注点1】flash的擦除性能远低于读写,相差几个量级

- 【关注点2】多线SPI访问特性 与 极限读取性能计算(一定要留有余量)

- 【关注点3】写保护区域设置 与 flash排布设计(只读 和 易变、可变区域 做隔离)

- 【关注点4】3/4字节地址切换问题,为满足超16M的容量空间。

- 三、常见问题与调试方法(待补充)

- 常见开机失败---3/4字节地址切换问题

- 常见读取性能差---中间缓存/时钟偏低

- 常见写数据概率失败---硬件链路设计问题信号干扰

- 常见读取数据概率失败---管脚驱动电流不够

- 参考资料:

一、Flash基本概念

存储器介绍与Flash在其中定位—非易失存储器类别中嵌入式领域常见设备

存储器常见分类类型:

1、易失性存储器:

RAM(Random Access Memory) 随机存取存储器。直接对字节地址进行随机读写,速度快,掉电丢失,用于存储运行数据或代码。包含DRAM(Dynamic Ram需要定时刷新)和SRAM(Static Ram 有电源不需要刷新)两种。

2、非易失存储器:

NVM(non-volatile memory) 断电数据不丢失。常见类型:

1)OTP(One Time Programmable)一次性可编程存储,程序烧入后不可再次更改和清除;

2)EPROM(Erasable Programmable ROM) 可擦除可编程只读存储器,利用高电压写入,曝光于紫外线抹除清空。

3)EEPROM(Eraseable programmable read only memory)电可擦编程只读内存,类似EPROM,抹除方式使用高电场。

4)Flash memory快闪存储器,读写速度和容量上要远远高于E2PROM,价格也便宜的多,嵌入式领域常用存储。

Flash的典型分类—NorFlash(贵/容量小/读快写慢)与NandFlash(便宜/容量大/读慢写快)

NOR和NAND是市场上两种主要的非易失闪存技术。NAND一般以存储数据为主,晶片容量大,容量可以达到2Gb甚至更大,读取块形式通常一次512个字节,采用这种技术的Flash比较廉价;NOR一般以存储程序代码为主,又称为Code Flash,采用内存的随机读取技术,可让微处理器直接读取,容量较低。

Flash的基本 存储和 读 写 擦原理—电荷是否超过特定阈值来表示0(低表示1)

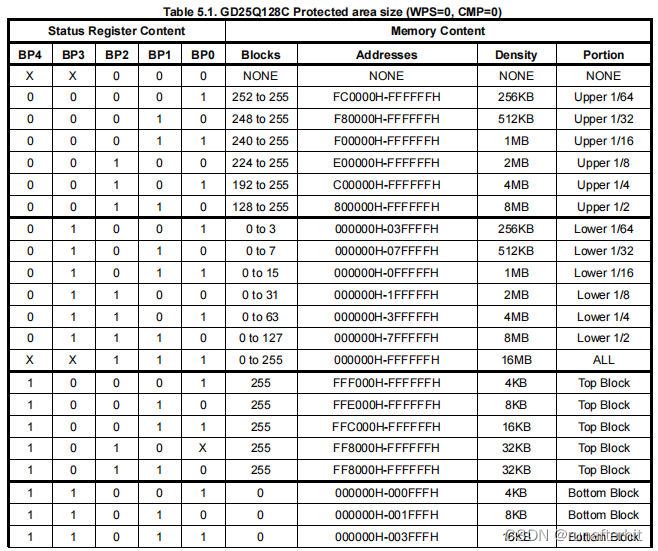

1)存储原理:数据在Flash内存单元中是以电荷(electrical charge) 形式存储的。闪存的存储单元为三端器件,源极、漏极和栅极。栅极与硅衬底之间有二氧化硅绝缘层,用来保护浮置栅极中的电荷不会泄漏,使得存储单元具有了电荷保持能力。

2)擦写原理:NAND型闪存的擦和写均是基于隧道效应,电流穿过浮置栅极与硅基层之间的绝缘层,对浮置栅极进行充电(写数据-设置0)或放电(擦除数据-设置1)。NOR型闪存擦除数据仍是基于隧道效应(电流从浮置栅极到硅基层),但在写入数据时则是采用热电子注入方式(电流从浮置栅极到源极)。

3)读取原理:依据有无电荷读取存储的数据,当浮置栅极有电荷时,源极和漏极可以导通,读取到的bit是0;擦除后浮置栅极无电荷,源极和漏极不能导通,读取的bit是1;

二、nor flash关键特性理解(以 GD25Q128介绍)

基本特性介绍—容量、访问接口、读写速度、擦除性能、写保护

容量:存储总量128Mbit(16Mbyte);

擦除性能:支持按4KB sector擦除(400ms) 或者 32KB(1S)/ 64KB(1.2S) block擦除,寿命支持10万次擦写,支持3字节4字节地址模式。

读写性能::访问方式SPI,最大支持4线访问80M时钟读写(数据传输320Mbits/S),支持写保护控制;

【关注点1】flash的擦除性能远低于读写,相差几个量级

flash的读写都是通过时钟CLK配置IO完成,可以通过提升时钟大小,构建多线IO来提高访问速度,如GD25Q128最大支持4线访问80M时钟读写(数据传输320Mbits/S)。但是擦除时不取决于时钟大小,也没有多线的概念, 完全由器件本身性能决定,如按4KB擦除要400ms,最快按64KB单元要1.2S(约0.4Mbits/S)和读取理论数据320Mbits/S相差几百倍。

【关注点2】多线SPI访问特性 与 极限读取性能计算(一定要留有余量)

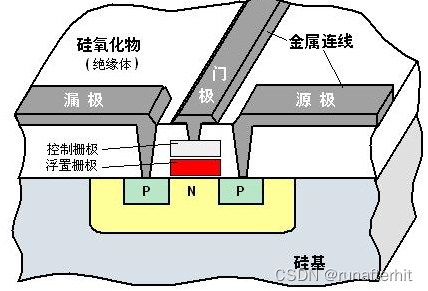

很多flash SPI器件都支持多线访问,即把部分IO作为数据SO或SI来支持多线并行读取。如GD25Q128用4线读取的时候,把SI、SO、WP写保护、HOLD都作为读取IO,可以一次CLK读取4个bit数据。

多线读取和理论值往往有一个损失率,0.5% 甚至可以到 15%(有非常多因素)。我们先算一下理论极限速度。

1)假如SPI时钟为100M = 100x10 ^ 6x4线传输 = 400 * 10 ^ 6 bit / S= 47.68MB / S。

2)再进一步,每次发送一次命令需要先发cmd+addr+Dummy(共20个CLK周期)然后读取,因此一次连续读取nByte(2n个时钟周期)确定了利用率,假如1次读取64个= 47.68MB/S * (2x64 / (2x64+20)) = 41.23MB/S;假如一次读取1M数据就还是47.68MB/S;

3)再进一步,实际测量波形发现大量数据读取过程CLK还是间歇性的,并不是完整连续的。这里引入因素也很多,SPI控制器从flash读取数据fifo是有深度的,当读取后 需要CPU或者DMA搬移走。特别是用CPU搬移的时候,很可能还涉及一些中间缓存buffer上下文,到目标sram可能会再搬移一次导致时间更长。

在计算耗时的时候,一定要根据系统进行排除并留有余量,不要简单按理论值计算。

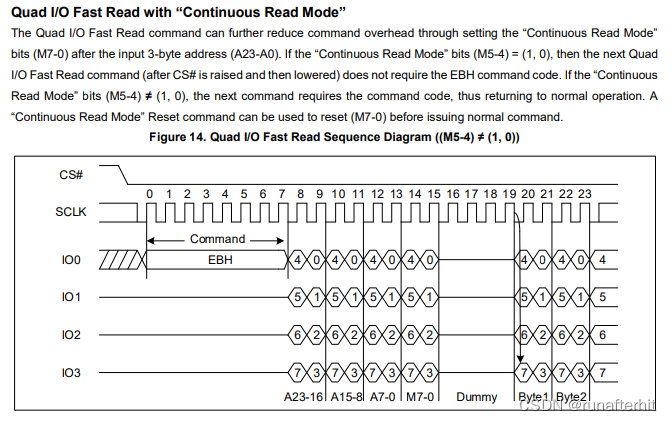

【关注点3】写保护区域设置 与 flash排布设计(只读 和 易变、可变区域 做隔离)

flash提供写保护区域设置,通过状态寄存器进行设置。如下类似,可以按 保护 首部或者尾部1/x、或首部 或者 尾部 固定大小block。也引导我们方案设计的时候 把只读区域 和 易变、可变区域 做隔离。

【关注点4】3/4字节地址切换问题,为满足超16M的容量空间。

容量低于16MByte的nor flash,一般是3字节模式:cmd+addr0+addr1+addr2,因为3个字节地址表示范围:0xffffff为16M内容。超过16M的时候,就需要用到4字节地址cmd+addr0+addr1+addr2+addr3。

注意点是:部分芯片bootrom不支持4字节地址模式,默认按3字节和nor flash通信,如果切换到4字节后重启就会导致bootrom启动失败。这里的解决方案是 软件在reboot前主动切换到3字节,但是不能解决主芯片硬重启的情况,因此更好的方法是硬件上调整供电控制 让 主芯片和norflash同步reset。一旦主芯片被复位下电norflash也下电,让二者都回到3字节模式,就可以正常启动了。

三、常见问题与调试方法(待补充)

常见开机失败—3/4字节地址切换问题

常见读取性能差—中间缓存/时钟偏低

常见写数据概率失败—硬件链路设计问题信号干扰

常见读取数据概率失败—管脚驱动电流不够

参考资料:

GD25Q128datasheet:https://www.gigadevice.com/zh-hans/flash-memory/gd25q128e/