linux 中 PCIE 中断映射机制

PCIE 中断映射机制

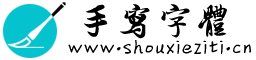

1、 PCIE 中有三种中断方式, MSI,MSI-X 和INTx

PCIe总线继承了PCI总线的所有中断特性(包括INTx和MSI/MSI-X),以兼容早期的一些PCI应用层软件。

PCI总线最早采用的中断机制是INTx,这是基于边带信号的。

后续的PCI/PCI-X版本,为了消除边带信号,降低系统的硬件设计复杂度,逐渐采用了MSI/MSI-X(消息信号中断)的中断机制。

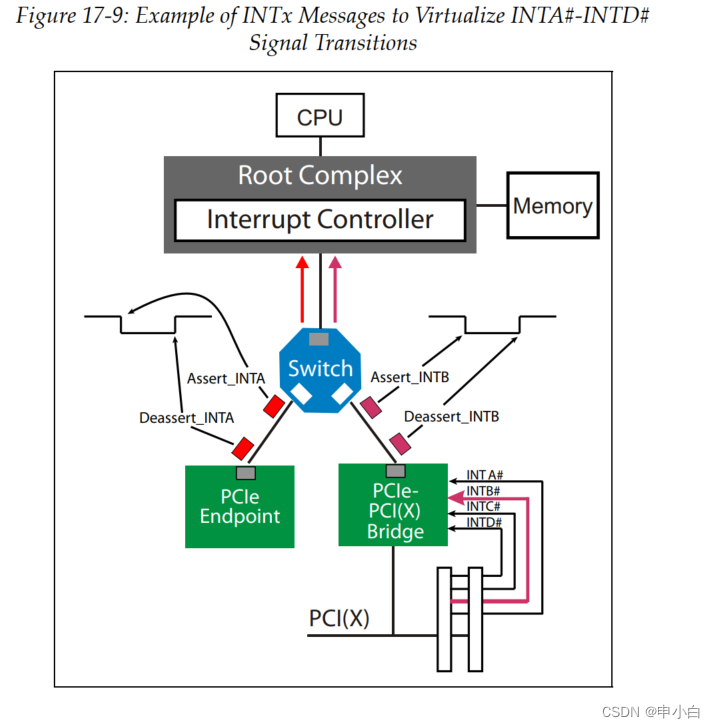

需要注意的是PCIE 继承了INTx 中断,并没有采用边带信号,而是用了Message TLP 的方式

另外一点, PCI规范中MSI和MSI-X都是可选的功能。但从PCIe规范开始,要求PCIe设备必须支持64位的MSI或者MSI-X。尽管1个PCIe设备可能同时支持Virtual INTx#/MSI/MSI-X,系统软件必须只Enable其中一种中断机制。

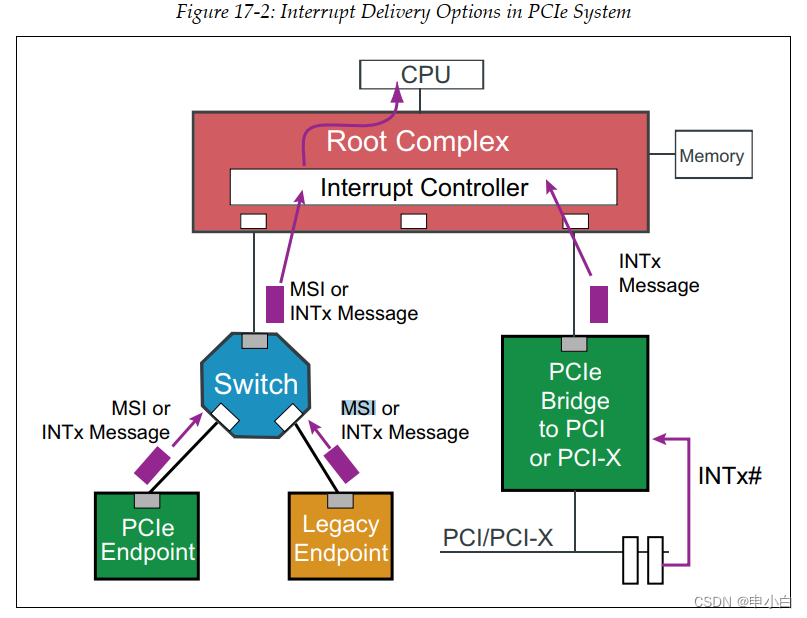

INTx 中断:

INTx一般被称为传统的(Legacy)PCI中断机制,每个PCI设备最多支持四个中断信号(边带信号,INTA#、INTB#、INTC#和INTD#)

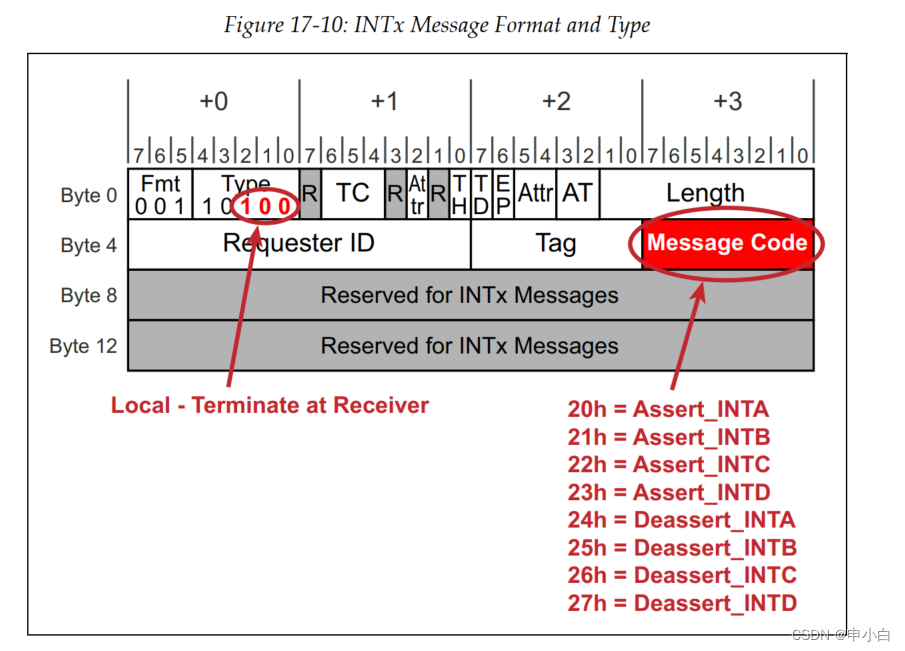

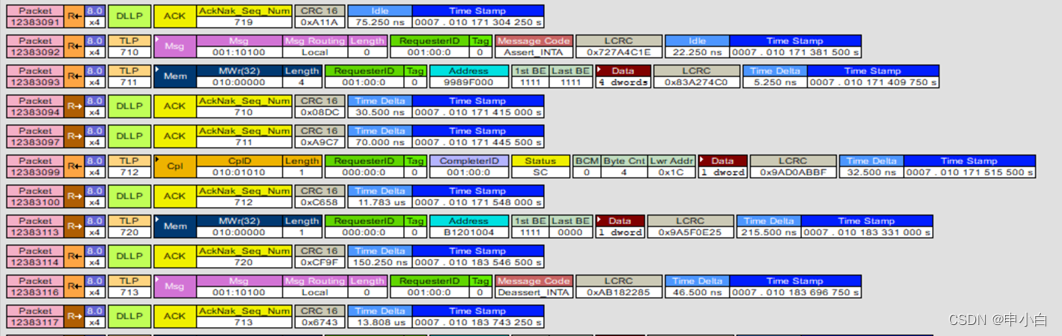

PCIE 中使用Message 来实现INTx 中断, 具体实现如下(Assert_INTx消息表示INTx信号的下降沿。Dessert_INTx消息表示INTx信号的上升沿):

从协议分析以上可以看到, 由于INTA 是电平信号,所有用Assert_INTA Msg 和Deassert_INTA Msg 来表示, 两个Msg之间的时间,对应的就是INTA 的电平长度

MSI 中断:

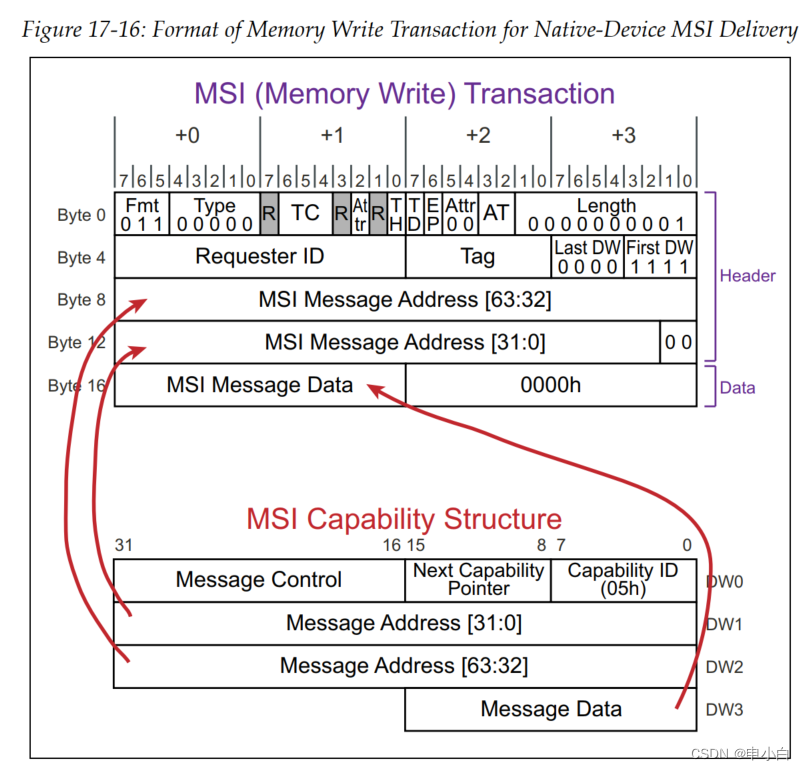

MSI 中断并不是Message TLP, 而是Memory Write TLP 。

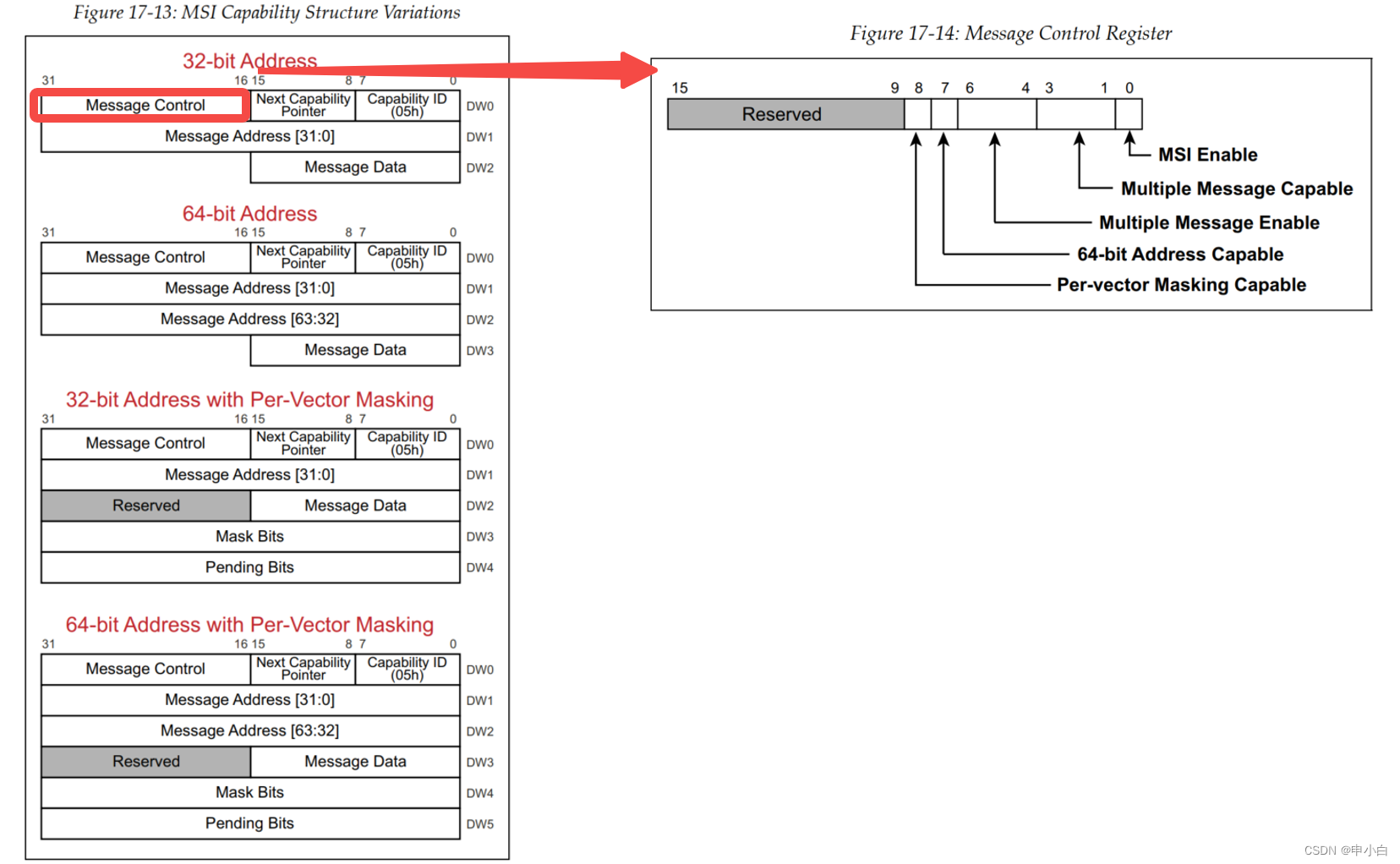

MSI capability 的结构体,在configure space 中格式如下, 其中Capability ID 0x05h 表示是MSI capability:

这边需要讲一下MSI (Memory Write) TLP 是由EP 发给RC 的,RC 向EP 的configure space中,填写 MSI capability 中的Message Address和Message Data。

EP 获取configure space 中的MSI capability 中的Message Address和Message Data, 将这个信息填充到MSI Memory Write TLP 中, 产生中断后,发给RC。

注: 在x86 架构中, 0xFEExxxxx 的地址APIC (Advanced Programmable Interrupt Controller高级可编程中断控制器) 的地址, EP 会将MSI 的MWr TLP 发给它,由它向x86 上报中断。

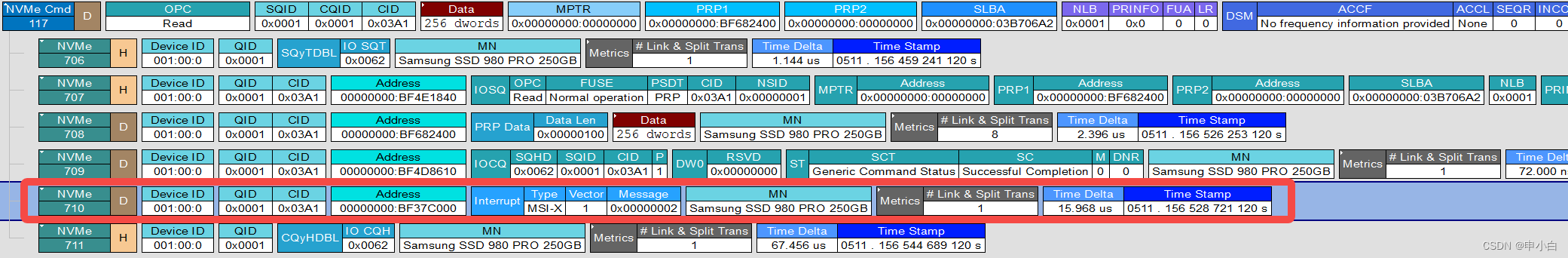

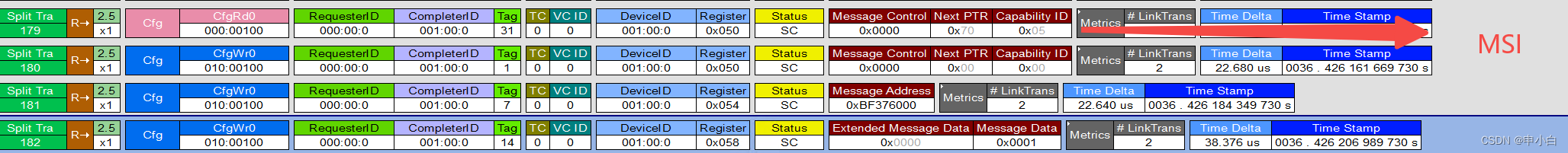

下面给出了MSI 的例子,MSI capability Structure 如下, Message address 为0xBF376000, Message data 为0x01

发送MSI Mwr TLP, 会获取MSI capability Structure中的地址和data, 然后发给host, 具体如下:

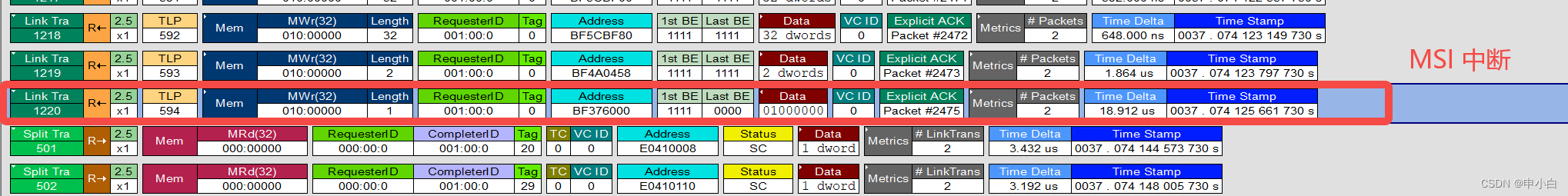

MSI-X 中断:

1)为什么需要MSI-X中断

一、MSI最大只支持32个中断,在很多应用中32个中断是不够的,因此引进了MSI-X, MSI-X 最大支持2048个中断可以满足各种应用的需求。

二、MSI机制下每个PCI Function的所有中断向量都共用1个Message Address,无法将其分配到不同CPU以实现中断服务在CPU间均衡分配

三、MSI机制下每个PCI Function的所有中断向量都是连续的,在某些平台连续的中断向量意味着同样的中断优先级,无法满足区分中断优先级的需求

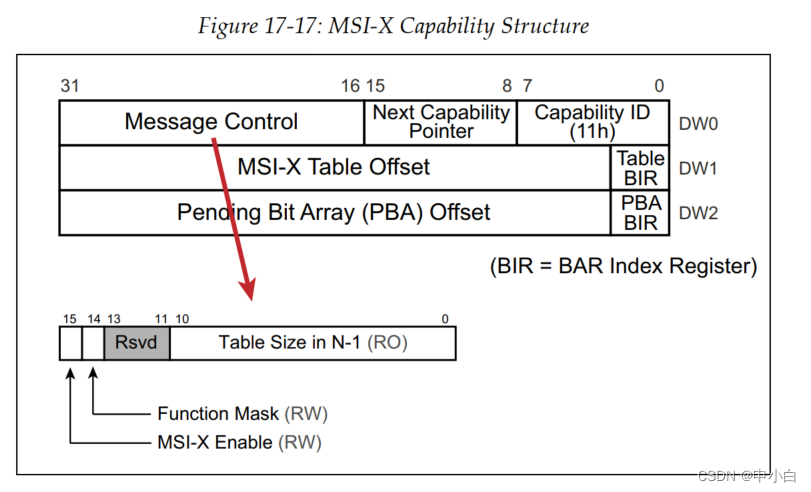

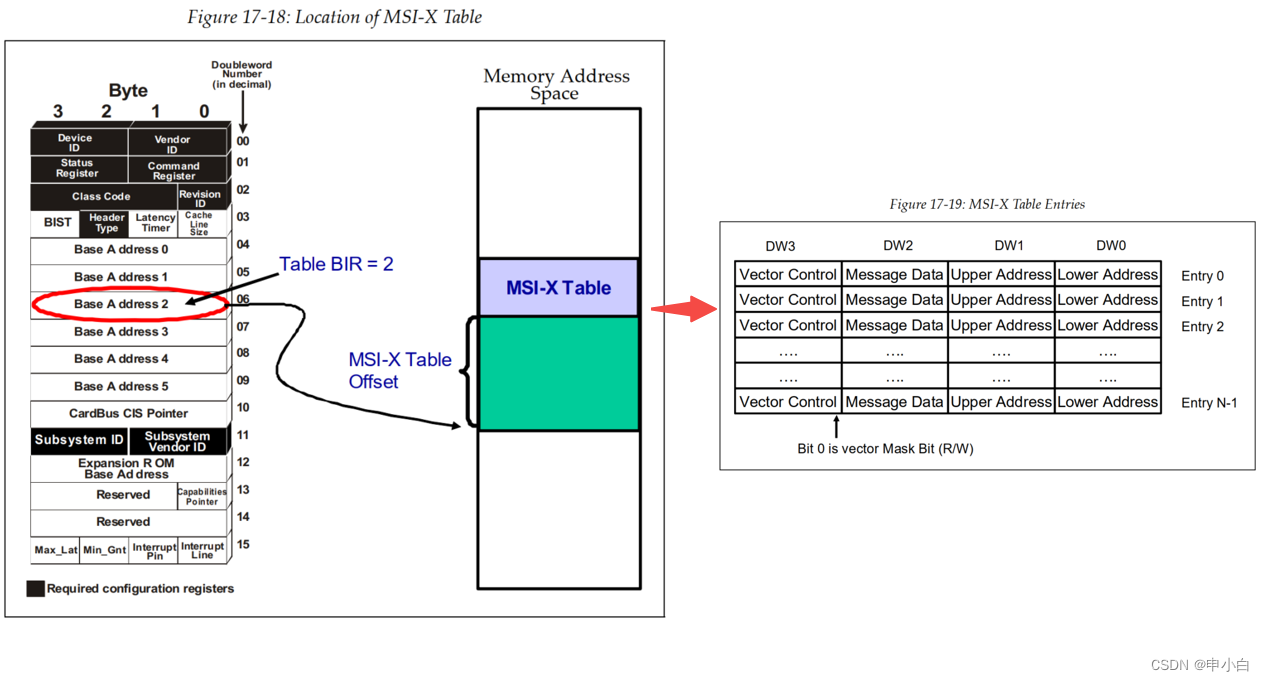

Table BIR(BAR Indicator Register)

基地址指示寄存器,该字段存放MSI-X Table所在的位置,PCIe总线规定,MSI-X Table存放在BAR空间中,该寄存器指示使用BAR0~BAR5寄存器中的哪个空间存放MSI-X Table,该字段由3位构成,3’b000 ~ 3’b101分别对应BAR0 ~ BAR5。

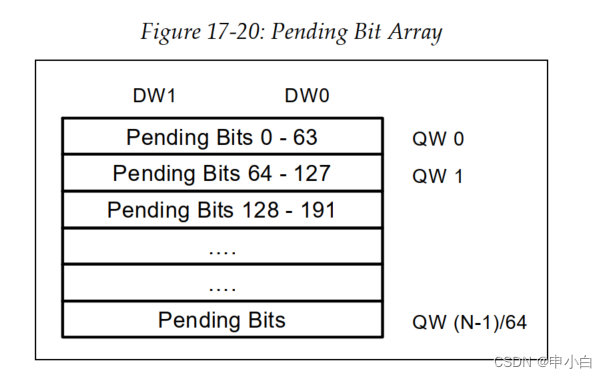

Pending Table

在Pending Table中,一个Entry由64位组成,其中每一位与MSI-X Table中的一个Entry对应,即Pending Table中的每一个Entry与MSI-X Table的64个Entry对应。与MSI机制类似,Pending位需要与Per Vector Mask位配置使用。

当Per Vector Mask位为1时,PCIe设备不能立即发送MSI-X中断请求,而是将对应的Pending位置1;当系统软件将Per Vector Mask位清零时,PCIe设备需要提交MSI-X中断请求,同时将Pending位清零。

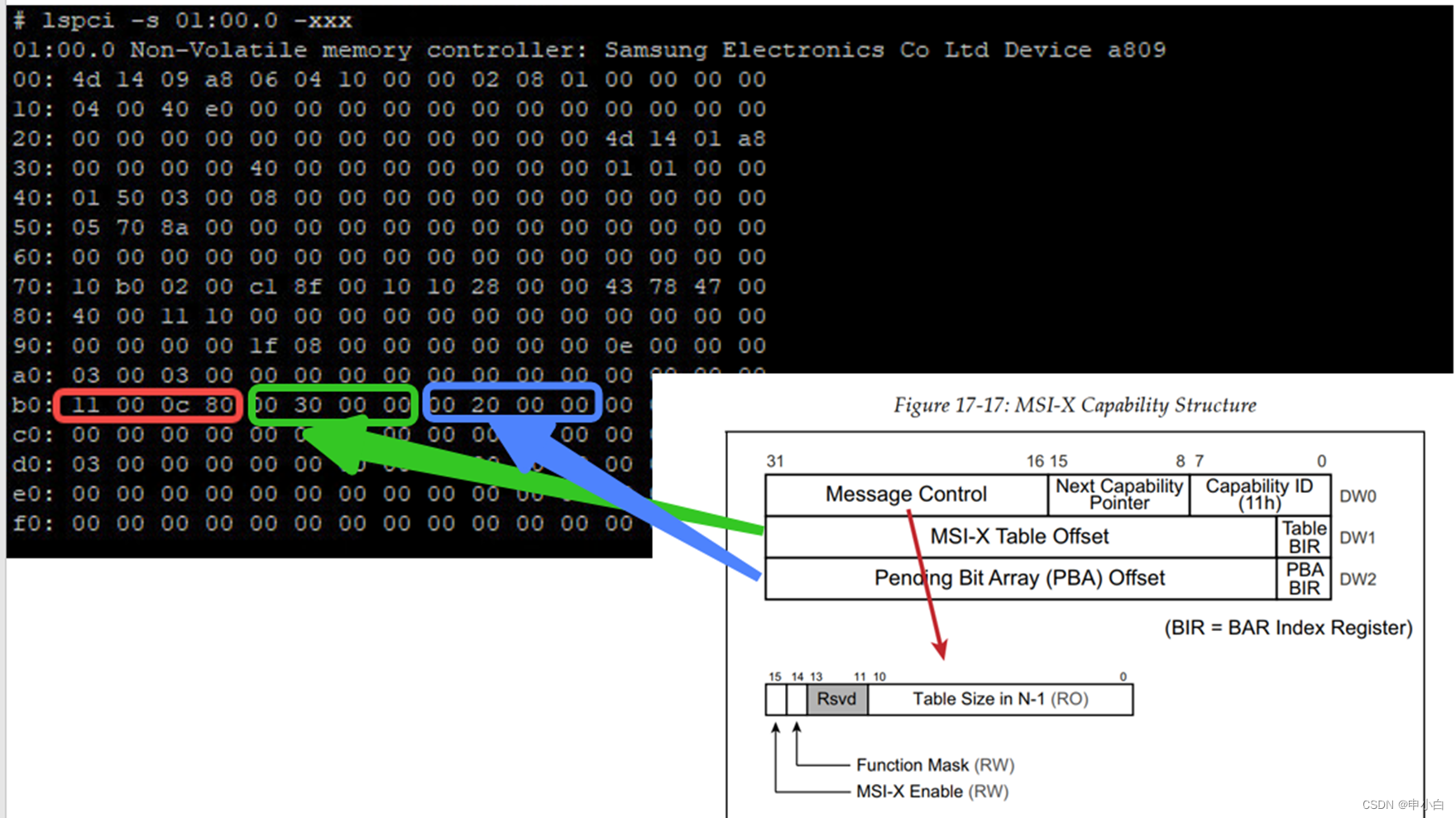

具体例子如下: 从device config spec 可以找到MSI-X Capability structure

以NVME 为例,更新MSI-X Table Entries:

配置Address (0x00000000 BF37c000) 和 Message Data (0x00000001), 设置Vector Control 的中断Mask bit(bit 0),所以就是4个Dword

配置Address (0x00000000 BF37c000) 和 Message Data (0x00000002), 没有设置Vector Control 的中断Mask bit,所以就是3个Dword

发送MSI-X 的MWr TLP, 向地址0xBF37c000 发送data 是0x2的中断