数字IC设计、验证、FPGA笔试必会 - Verilog经典习题 ( 七)求两个数的差值

数字IC设计、验证、FPGA笔试必会 - Verilog经典习题 (七)求两个数的差值

🔈声明:

😃博主主页:王_嘻嘻的CSDN博客

🧨未经作者允许,禁止转载

🔑系列专栏:牛客Verilog习题集

🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧

继续整理牛客网经典Verilog习题讲解,牛客网里除了最新的Verilog题库还有其它领域的经典笔试、面试题,大家快和我一起刷起来吧 点 击 跳 转

题目

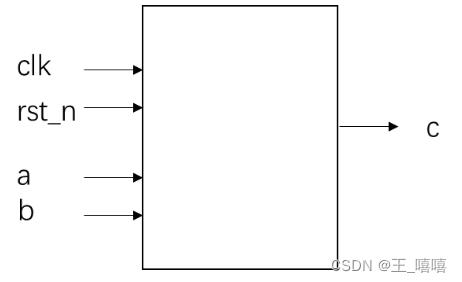

根据输入信号a,b的大小关系,求解两个数的差值:输入信号a,b为8bit位宽的无符号数。如果a>b,则输出a-b,如果a≤b,则输出b-a。

分析:

本题比较简单,a、b、c都是无符号数,只有一个输出c,根据a、b的大小关系决定是a-b或者b-a。

代码也没过多可关注的,不过建议新手朋友使用每一个多bit变量时,能将位宽描写清楚,便于后期修改或者review时,清楚每个变量的位宽。

题解:

`timescale 1ns/1ns

module data_minus(

input clk,

input rst_n,

input [7:0]a,

input [7:0]b,

output reg [8:0]c

);

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

c[8:0] <= 9'b0;

else if(a[7:0] > b[7:0])

c[8:0] <= a[7:0] - b[7:0];

else

c[8:0] <= b[7:0] - a[7:0];

end

endmodule