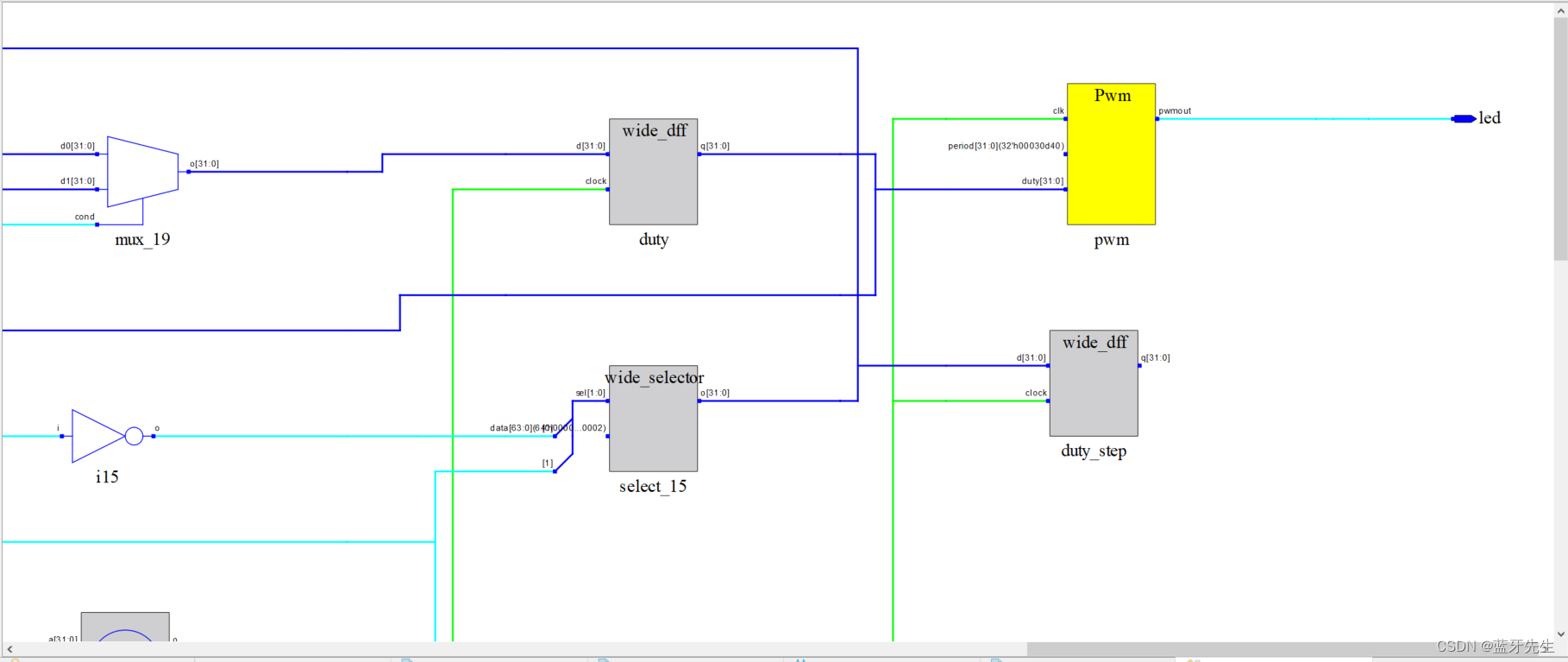

GW1NSR-LV4CQN48GC6/I5 FPGA呼吸灯

环境

pwm.v

$ cat pwm.v

module Pwm(

input clk,

input [31:0] period,

input [31:0] duty,

output pwmout

);

reg [31:0] counter;

reg r_pwmout;

always @(posedge clk) beginif(counter < duty) begin

r_pwmout = 1;

end

else begin

r_pwmout = 0;

endcase(counter)

default:

counter = counter + 1;

period:

counter = 0;

endcaseend

assign pwmout = r_pwmout;

top.v

$ cat top.v

module top(

input sys_clk,

input key1,

output led

);

parameter TIME_1MS = 1000;reg [31:0] duty;

parameter pwm_period = 200 * TIME_1MS;

Pwm pwm(sys_clk, pwm_period, duty, led);

reg [31:0] counter;

reg [31:0] duty_step;

reg modify_duty;

reg duty_dir;

always @(posedge sys_clk) begincounter = counter + 1;

case(counter % (TIME_1MS / 5))

0:

modify_duty = 1;

endcasecase(duty)

0:

duty_dir = 1;

pwm_period:

duty_dir = 0;

endcasecase(duty)

0 - pwm_period / 2:

duty_step = 10;

default:

duty_step = 2;

endcaseif(modify_duty) begin

if(duty_dir) begin

duty = duty + duty_step;

end

else begin

duty = duty - duty_step;

end

modify_duty = 0;end

end

原理图