【DDR3 控制器设计】(1)MIG IP 核的详解与配置

写在前面

本系列为 DDR3 控制器设计总结,此系列包含 DDR3 控制器相关设计:认识 MIG、初始化、读写操作、FIFO 接口等。通过此系列的学习可以加深对 DDR3 读写时序的理解以及 FIFO 接口设计等,附上汇总博客直达链接。

【DDR3 控制器设计】系列博客汇总篇(附直达链接)

目录

实验任务

实验环境

实验框图

配置 MIG 核

汇总篇

实验任务

学会如何根据手册配置 MIG IP 核中的参数、

实验环境

开发环境:Vivado 2018.2,

FPGA 芯片型号:xc7a100tffg484-2

DDR3 型号:MT41J256M16HA-125

实验框图

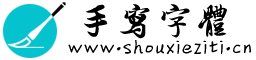

以下为 MIG 和 DDR 之间的连接框图,可以看到框图的左边是用户接口,中间是 MIG 核,右边是需要控制的 DDR 接口,用户只需要去配置使用 MIG 核,就可以对 DDR 进行控制读写等操作。

配置 MIG 核

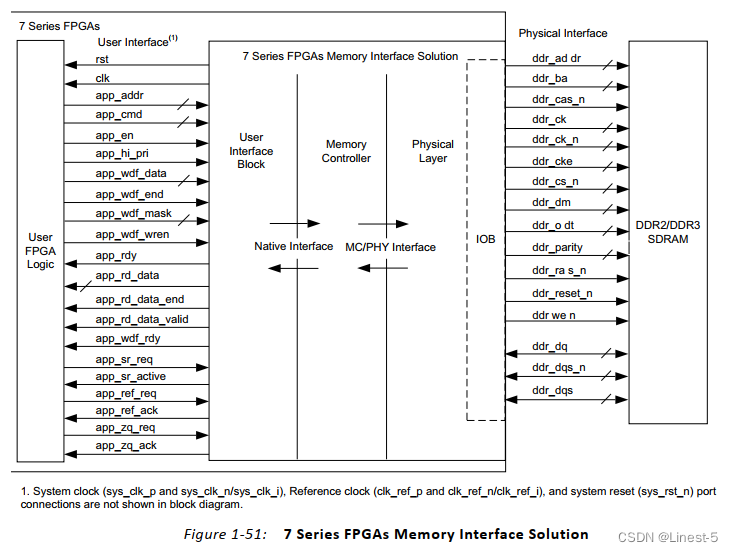

首先线创建一个工程,这个不详细说明了,然后在点击 IP Catalog 搜索 MIG,双击打开 IP 核配置界面进行配置。

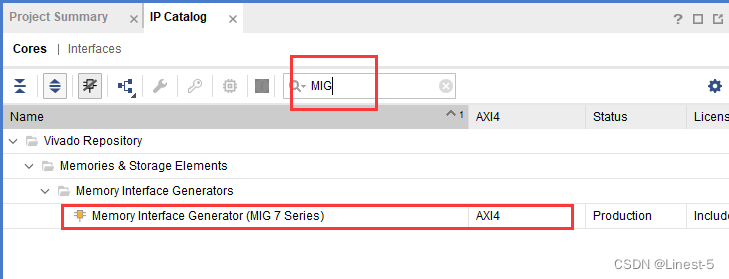

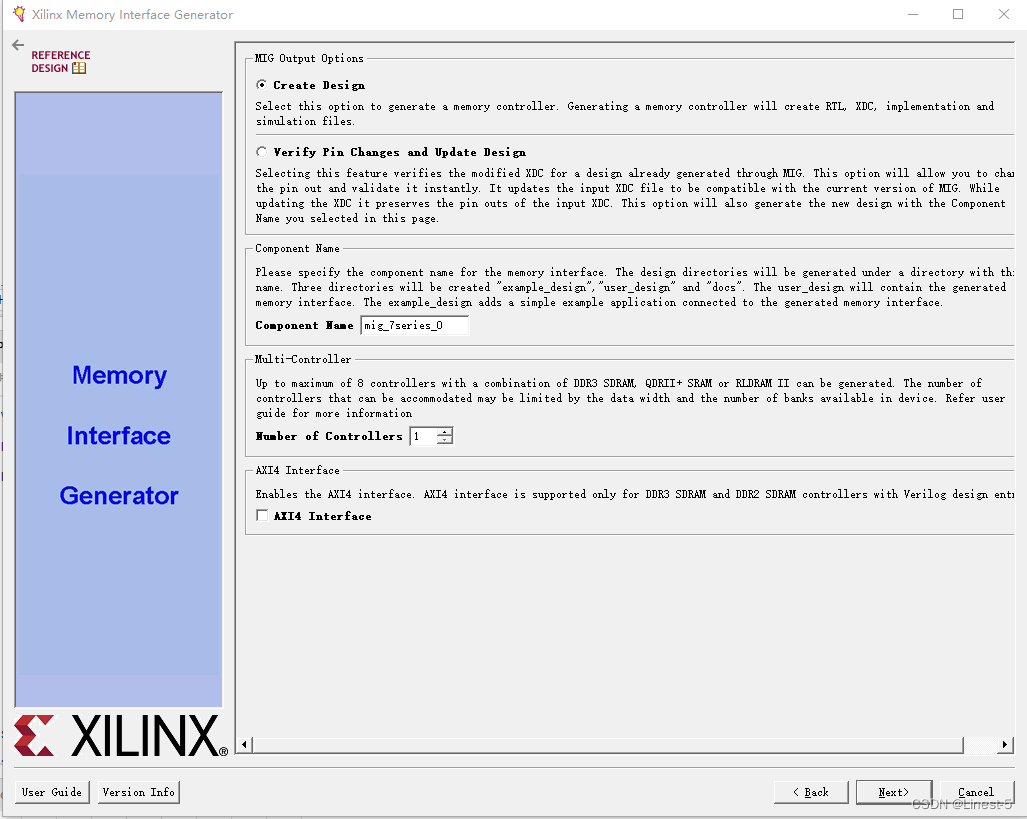

第一页

此页展示了所选用的 FPGA 型号等信息,直接next。

第二页

这页主要是配置基本信息。

- 创建一个新的工程设计

- 对 MIG 核进行命名

- 选择控制器的数量

- 是否选择 AXI4 接口

这里都保持默认即可。

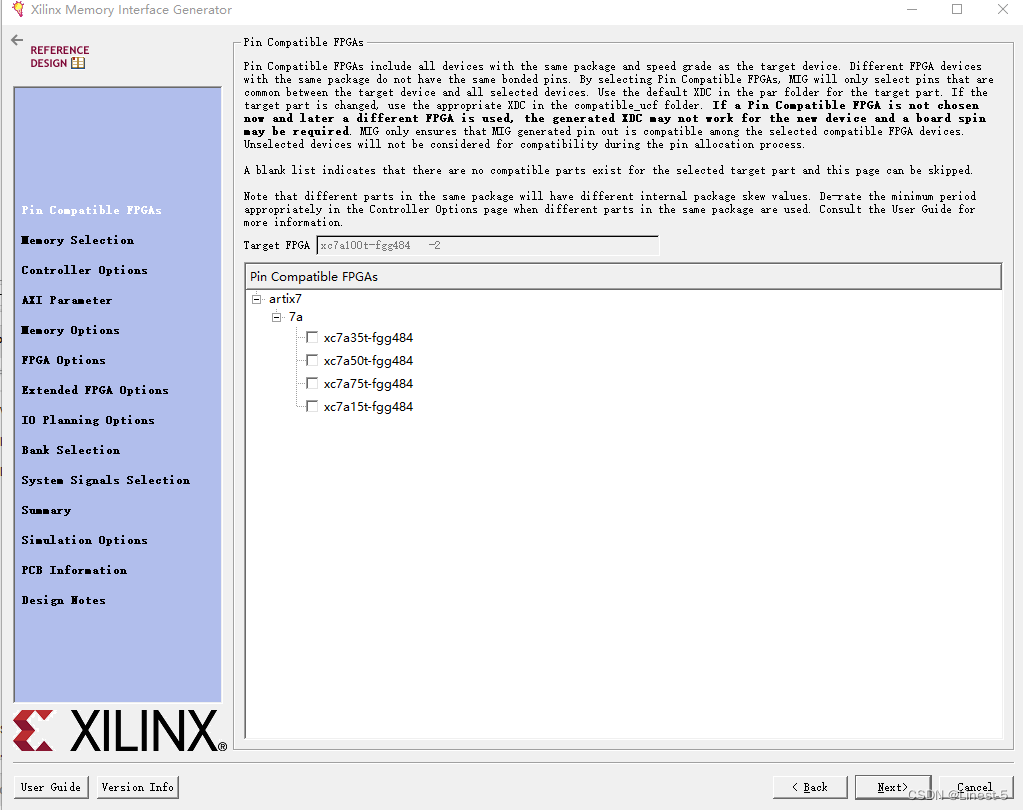

第三页

Pin Compatible FPGAs

此页面列出了所选系列中具有相同系列。如果从 MIG 工具生成的引脚需要与列表中 FPGA 连接,此选项应用于选择引脚分配的 FPGA 必须兼容。

这里建议直接不选 next。

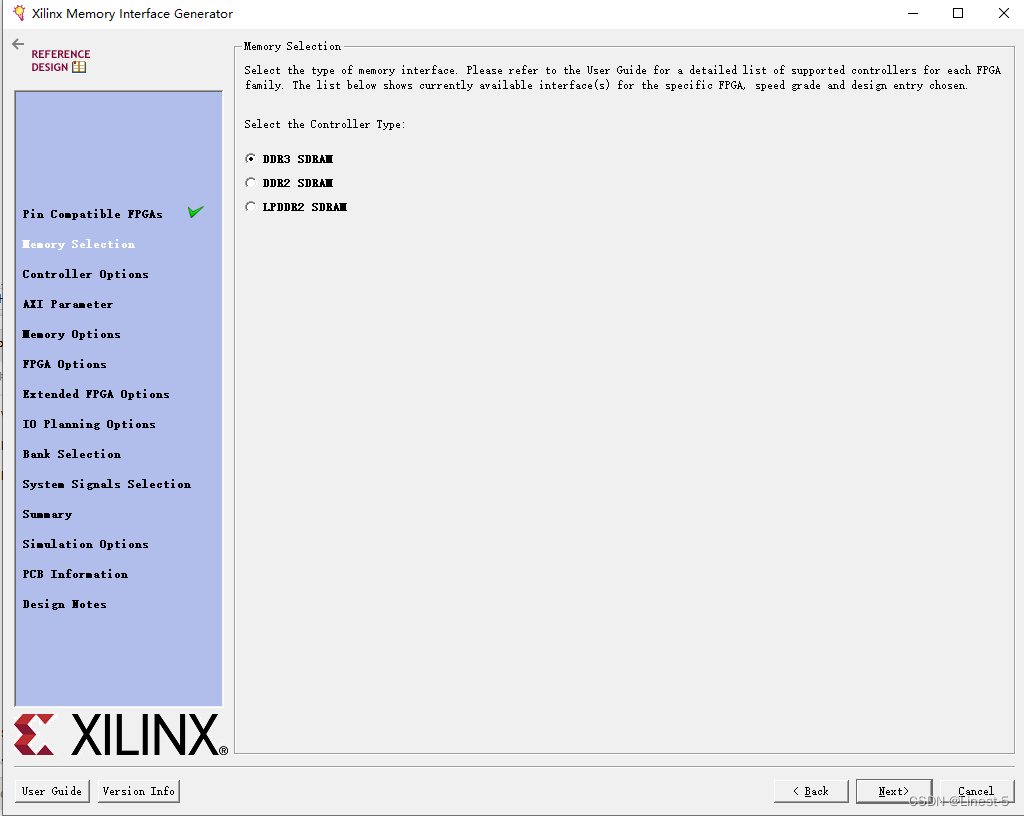

第四页

Memory Selection

此页面显示所选 FPGA 系列支持的所有存储类型,我使用的 FPGA 支持 DDR3、DDR2 和 LPDDR2,根据 FPGA 的类型可能支持的存储类型更多。本次实验对为 DDR3 初始化测试,因此选择 DDR3 即可。

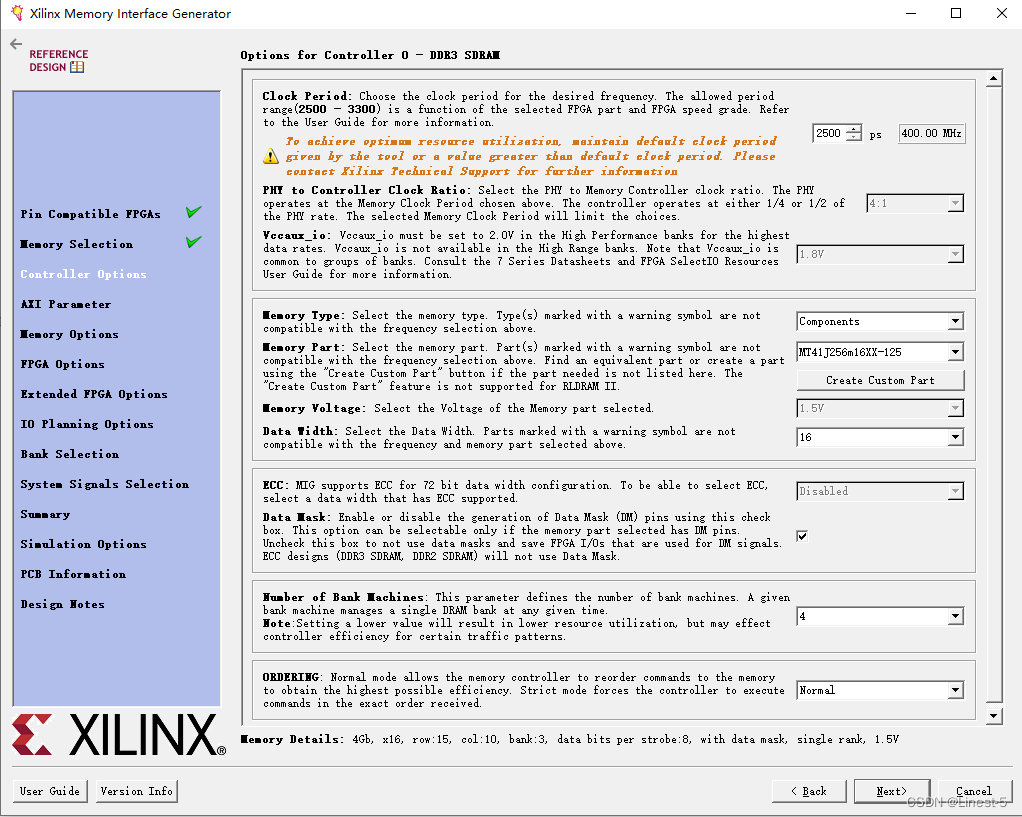

第五页

Controller Options

Clock Period:用作 DDR 的工作时钟,由于 DDR 是双边沿采样,所以实际工作频率为此时钟频率的两倍。

PHY to Controller Clock Ratio:配置物理层的比例(内存)控制器时钟频率和用户界面时钟频率。 2:1 比例的用户接口数据总线宽度是 MIG 内存接口宽度的 4 倍,比如 MIG 中配置的数据位宽是 16 位,而 DDR 双边采样,所以用户接口是 MIG 内存接口的 4 倍即数据位宽为 64 位,同理可以得到如果设置为 4:1 则是 8 倍的数据位宽即数据位宽为 128 位。并且需要注意的是当 Clock Period 配置为 350MHz 以上时,目的可能是避免用户端的时钟过大。

Vccaux_io:高性能Bank供电电压。MIG 工具需要时自动选择1.8V。

Memory Type:选择内存类型,默认选择 components。

Memory Part:DDR3 的型号,根据自己的 DDR3 型号选择,我用的是 MT41J256M16HA-125。

Memory Voltage:DDR3 的供电电压,默认为1.5V。

Data Width:选择数据位宽值,这里选择16位宽。

ECC:只有 V 系列等才有的功能,这里默认不选用。

Data Mask:数据掩码。每一位表示屏蔽数据的 8 位,如前面设置的数据位宽为 16 位,则 Data Mask 的位宽为两位,0位表示屏蔽数据的低 8 位,1 位表示屏蔽数据的高八位。

Number of Bank Machines:Bank Machine 数量,这里默认 4 个即可。

ORDERING:表示 MIG 是否可以指令进行重新排序,选择 Normal 表示开启此功能,这样效率更高。选择 Strict 表示不开启此功能。

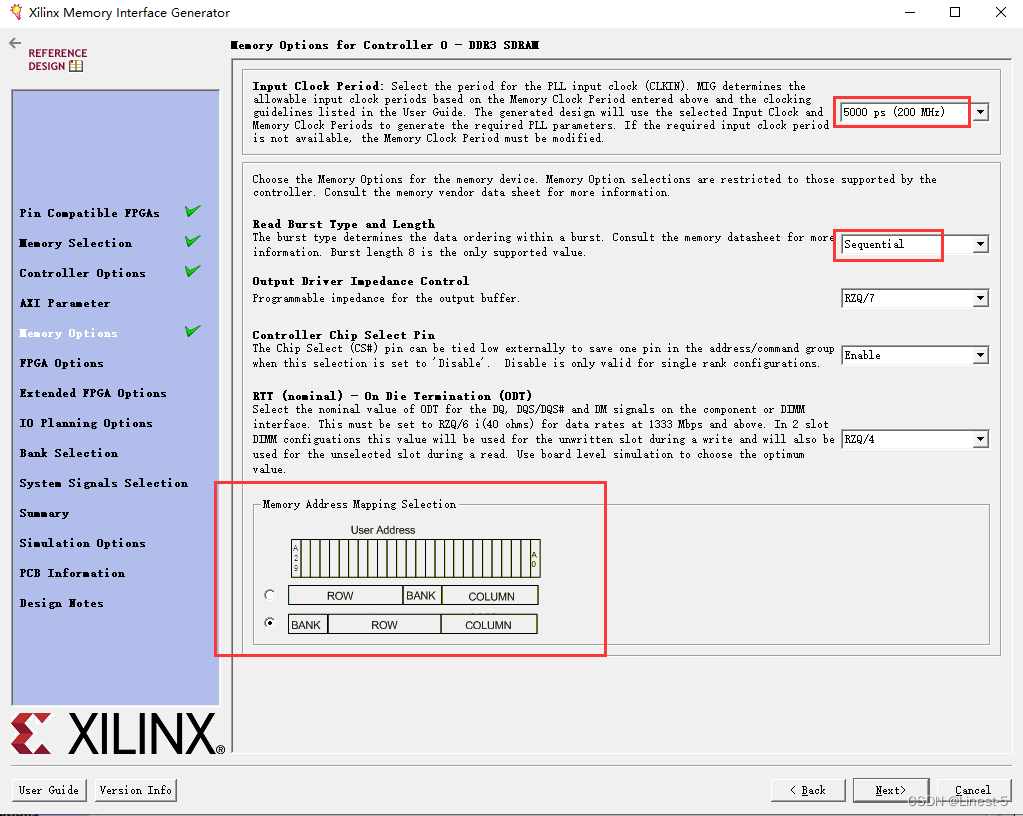

第六页

Memory Options

由于本实验没有用到AXI4接口,所以AXI Parameter选项卡没有涉及到。

Input Clock Period:MIG 核的输入时钟,外部输入时钟通过MIG核内部的锁相环倍频时钟到 Clock Period 时钟提供给 DDR3,此时钟为锁相环的输入时钟。这里设置为200MHz。

Read Burst Type and Length:突发类型和长度,选择Sequential:顺序突发,突发长度为 8。注意:只有DDR2和DDR3 支持突发长度8。

Output Driver Impdance Control:输出驱动器阻抗控制设置 DRAM 上的输出驱动器阻抗。列表的选项由所选的特定 DRAM 决定。 RZQ 为 240Ω。如果选择 RZQ/6,则输出驱动阻抗为 40Ω。这里选择 RZQ/7约为34.29Ω。

Controller Chip Select Pin:控制器片选管脚。默认选择 enable。

RTT(nominal):选择RZQ/4,保持默认即可。

Memory Address Mapping Selection

存储寻址方式的设置

第一种为先对一个 bank 的第一行的每一列完成访问,再去切换 bank 还是访问第一行,直到所有 bank 的第一行都访问完了,再切换到第二行访问,以此类推。

第一种为先对一个 bank 的第一行的每一列完成访问,再去切换到第二行每一列访问,直到第一个 bank 的都访问完了,再切换到第二个 bank 访问,以此类推。

两种访问方式的优缺点:

第一种方式可以对所有的bank同时给激活,在写入的时候就可以连续写入,这对于大量的数据的连续写入的情况比较占优,数据量至少大于等于SDRAM的一行。

第二种方式对于断续碎片式的数据写入比较占优。

这里选择第二种寻址方式。

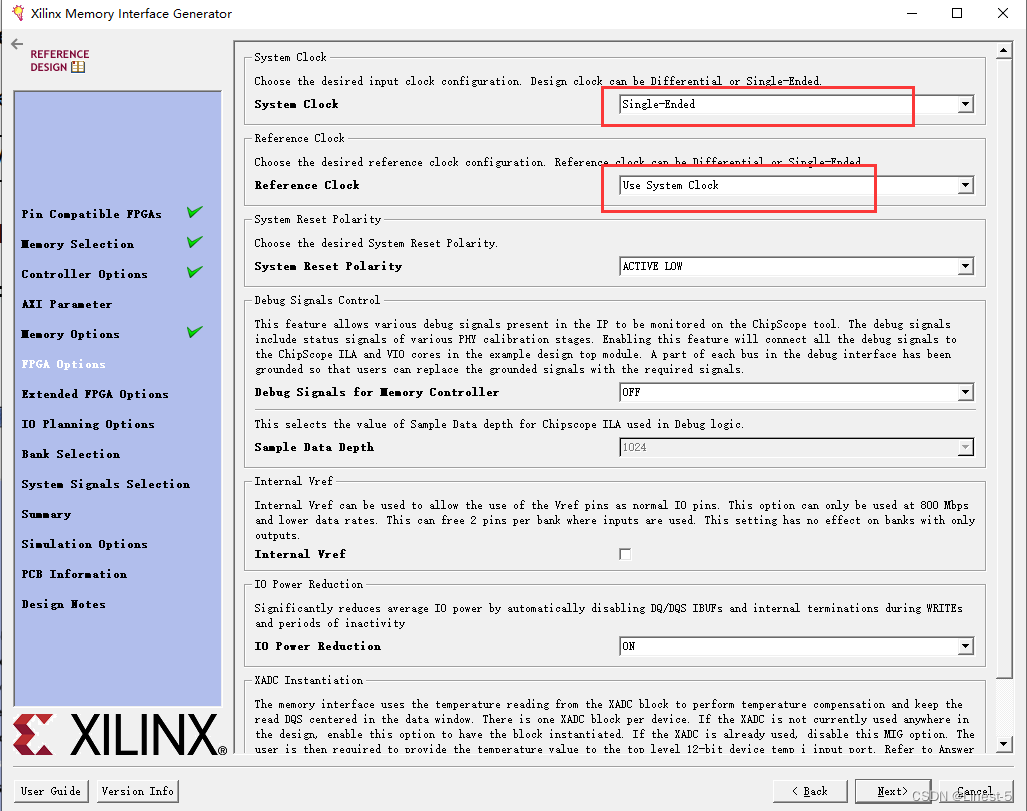

第七页

System Clock:系统时钟即MIG核输入的时钟,有 single_ended、deferential 和 no buffer 三种, single_ended 为来源于引脚的单端时钟, deferential为差分时钟, no buffer 为来源于 FPGA 内部的时钟。这里选择 single_ended。

注:差分时钟只有在输入和输出才会有这个概念,在芯片内部的时钟都是单端时钟。

Reference Clock:参考时钟有四种, 其中三种也为 Single-Ended、 Deferential 和 No Buffer, 另外一种为 Use System Clock,只有在 System Clock 时钟频率为 199MHZ~201MHz 时, 参考时钟才存在 Use System Clock选项。由于本实验的System Clock为200MHz,所以直接选用 Use System Clock。

System Reset Polarity:复位有效电平选择。选择“ACTIVE LOW”低电平有效。

Debug Signals Control:该选项用于控制 MIG IP 核是否把一些调试信号引出来,它会自动添加到 ILA,这些信号包括一些 DDR3 芯片的校准状态信息。选择 “OFF”,不需要让 IP 核生产各种调试信号。

System Reset Polarity:系统复位极性,这里默认为低有效。

Debug Signals for Memory Controller:选择此选项启用校准状态和用户端口信号端口映射到 example_top 模块中的 ILA 和 VIO。这有助于使用 Vivado Design Suite 调试监控用户界面端口上的流量特征。取消选择 Debug Signals Control 选项会保留调试信号在 example_top 模块中未连接,并且不生成任何 ILA/VIO 模块 IP 目录。此外,调试端口始终禁用功能模拟。这里选择不使用OFF。

Sample Data Depth:采样数据深度。因为不使用Debug,所有这里默认不可选。

Internal Vref Selection:内部 VREF 可用于数据组字节,以允许使用 VREF 引脚用于普通 I/O 使用。内部VREF仅应用于数据 800 MB/s 或以下的速率。这里不使用。

IO Power Reduction:此选项通过禁用 DQ 来降低平均 I/O 功率和 DQS IBUF 会在控制器处于空闲状态时自动执行。默认选择ON。

XADC Instantiation:启用后,此选项指示 MIG 内核实例化XADC 和温度监控器功能的温度轮询电路(见温度监视器)。如果已使用 XADC,则可以禁用此选项设计中的其他地方。在这种情况下,设备温度必须定期采样并驱动到存储器接口顶层的 device_temp_i 总线上用户设计模块。如果 device_temp_i 信号未连接,则 XADC被实例化。否则 XADC 不会被实例化。默认选择 enable。

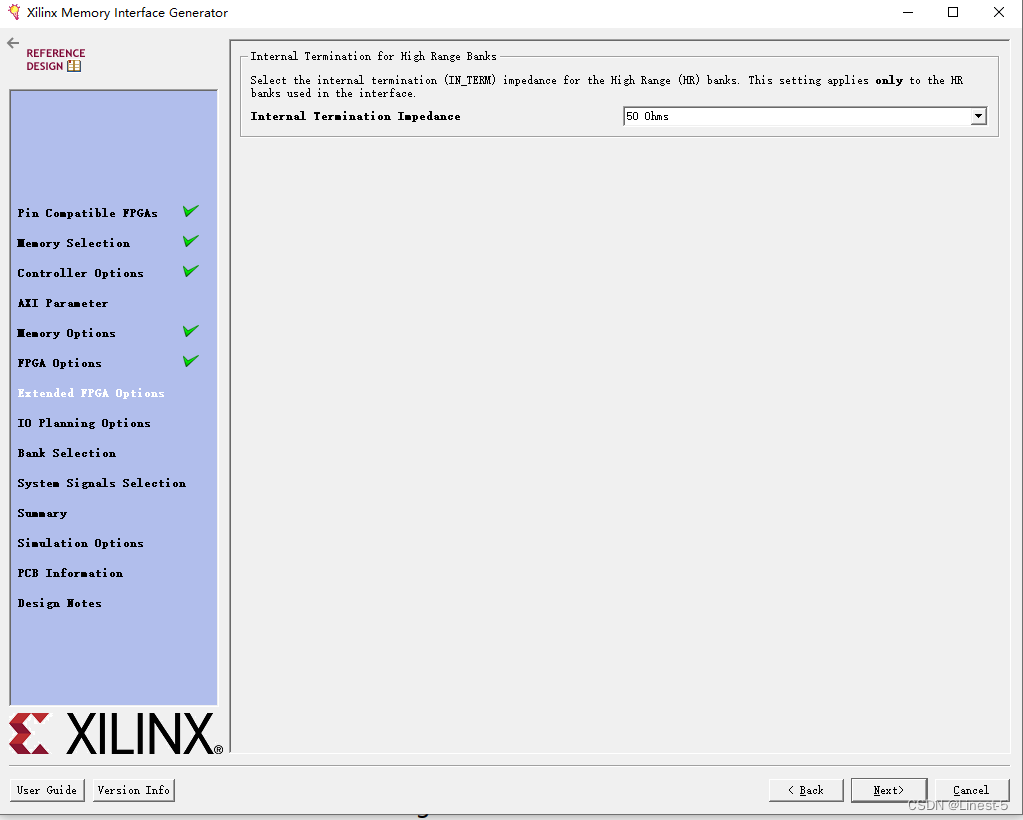

第八页

Internal Termination for High Range Banks

Internal Termination Impedance:内部终止选项可以是设置为 40、50 或 60Ω 或禁用。此选择仅适用于高性能Bank,默认选择50Ω。

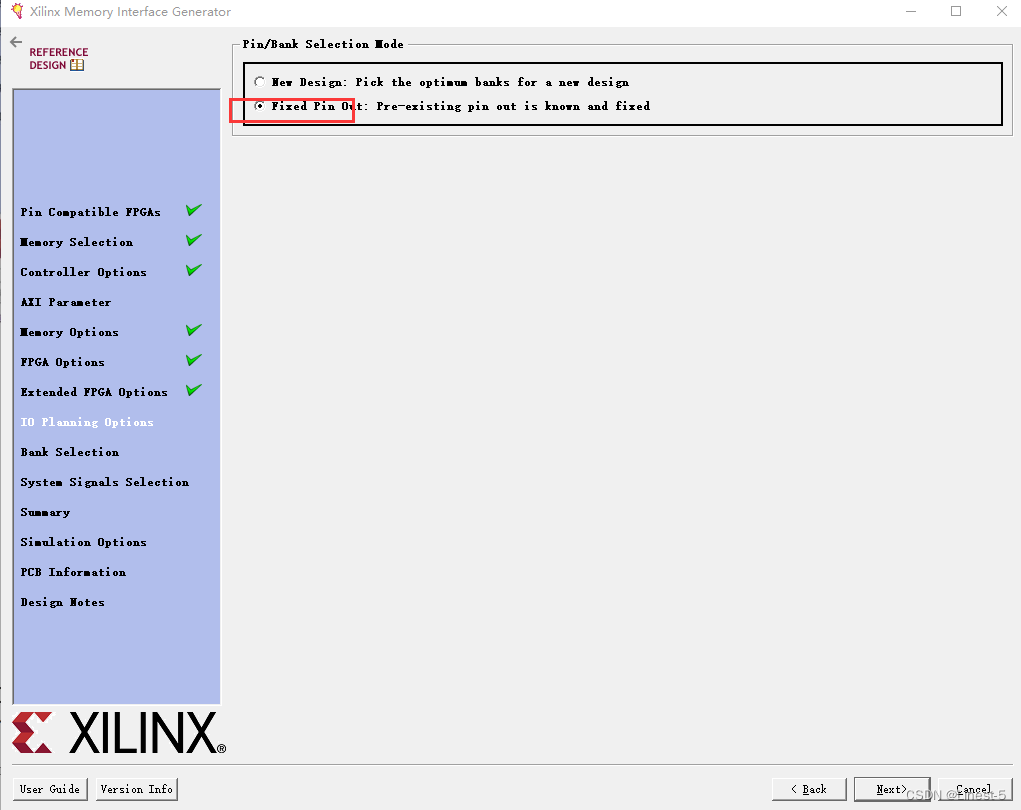

第九页

选择固定引脚,直接读出引脚绑定文件。

第十页

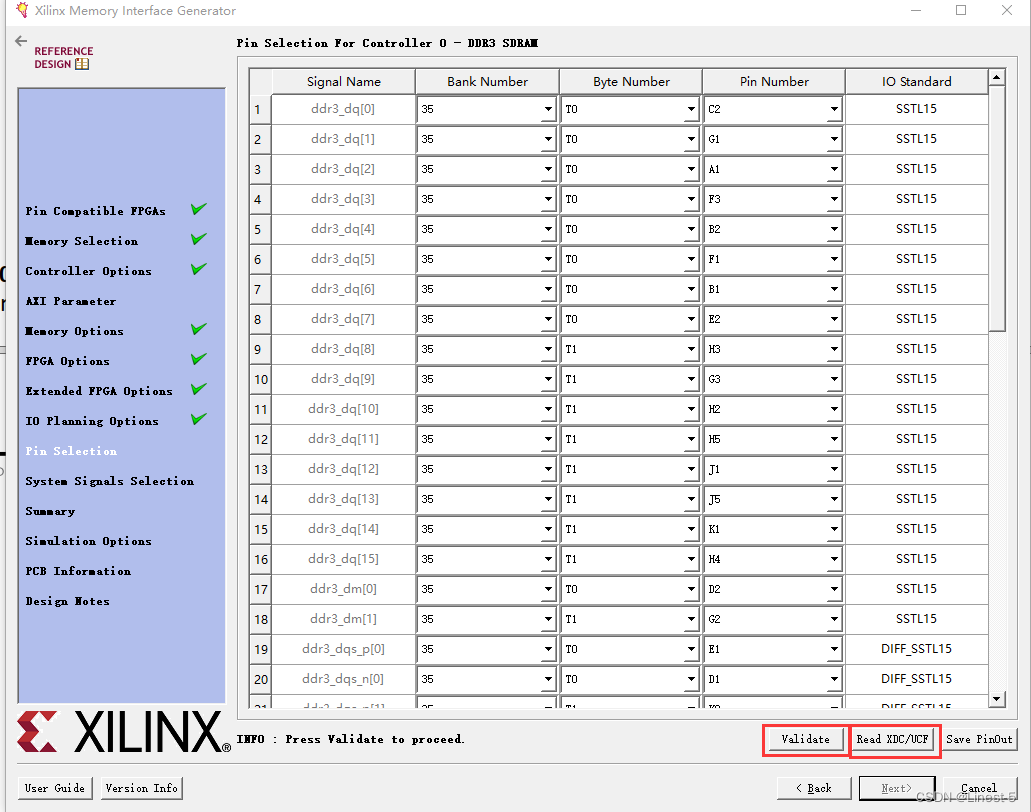

Pin Selection

点击read XDC/UCF文件,然后点击Validate->ok即可。

第十一页

System Signals Selection

sys_clk:这是内存接口的系统时钟输入,通常是连接到外部时钟源。单个输入或差分可以根据“ FPGA选项”页面中的系统时钟选择。sys_clk 输入必须与内存相同接口。如果此引脚与内存接口相同的 Bank 连接,则 MIG 工具选择与接口兼容的 I/O 标准,例如 DIFF_SSTL15 或 SSTL15。如果 sys_clk 未连接在内存接口 Bank 中,则 MIG 工具选择适当的标准,例如 LVCMOS18 或 LVDS。这里保持默认。

clk_ref:这是 IDELAY 控件的参考频率输入。clk_ref 输入可以在内部生成或连接到外部源。I/O标准以与 sys_clk 相似的方式选择。

sys_rst:这是可以在内部生成的异步系统复位输入或从引脚驱动。 MIG 工具为输入选择合适的 I/O 标准例如分别用于 HP 和 HR 组的 LVCMOS18 和 LVCMOS25。默认sys_rst 引脚的极性为低电平有效。

init_calib_complete:此输出表明内存初始化和校准完成并且接口可以使用。这 init_calib_complete 信号通常只在内部使用,但可以带如果需要,输出到引脚。

tg_compare_error:数据比较错误指示信号。

以上参数设定保持默认。

第十二页

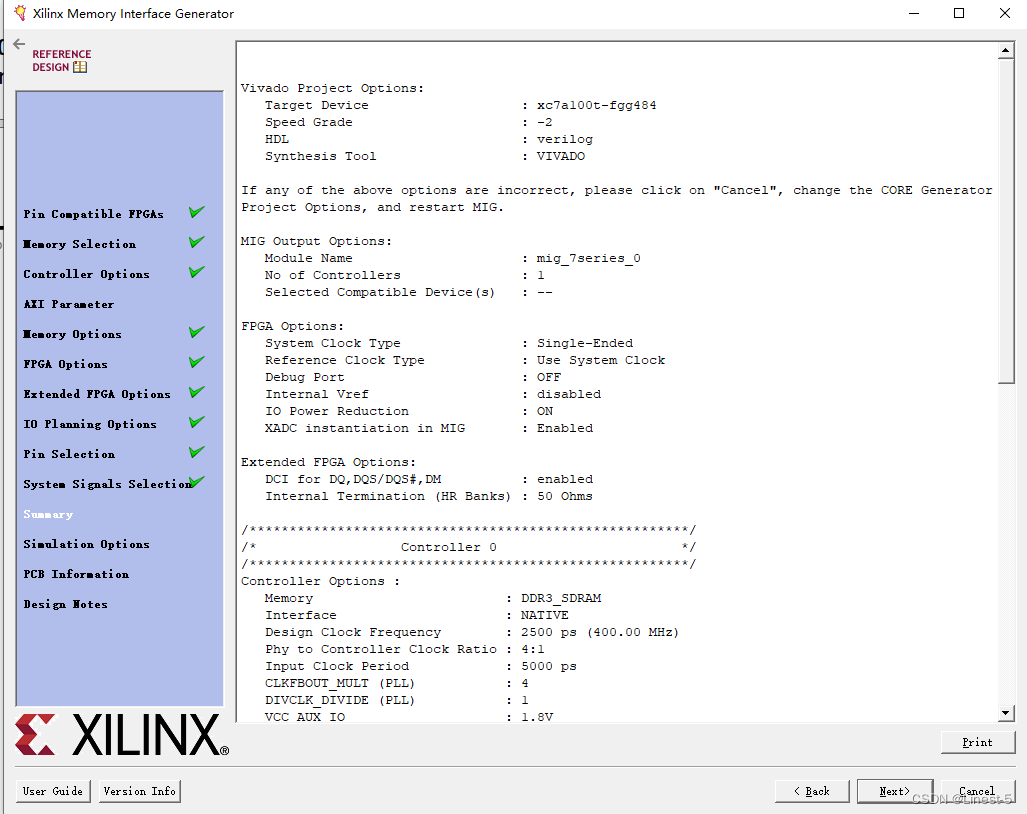

Summary

MIG配置的汇总页。

第十三页

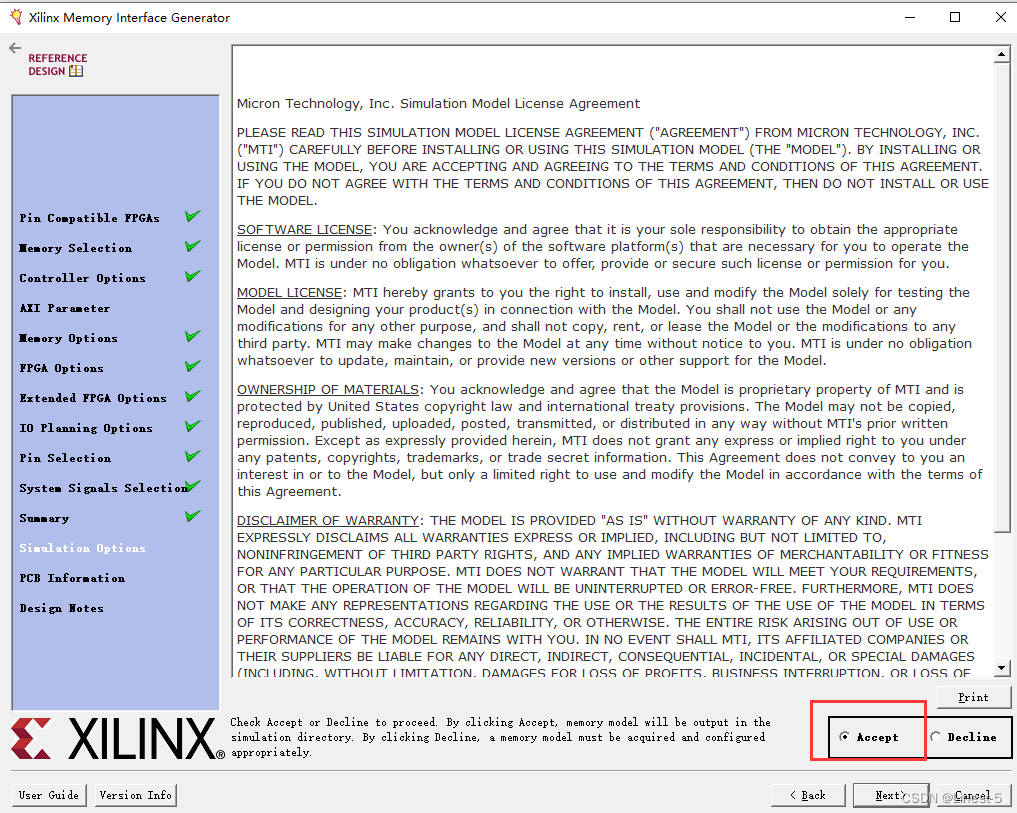

Simulation Options

选择 accept 点击 next。

随后一直点击next最后generate即完成 MIG IP 核的配置。

汇总篇

本系列为 DDR3 控制器设计总结,此系列包含 DDR3 控制器相关设计:认识 MIG、初始化、读写操作、FIFO 接口等。通过此系列的学习可以加深对 DDR3 读写时序的理解以及 FIFO 接口设计等,附上汇总博客直达链接。

【DDR3 控制器设计】系列博客汇总篇(附直达链接)